Purpose

A functional development of a specified, undesired event using logical symbols to denote the relationships between components and the undesirable event. The Fault Tree analysis will produce a graphical model of various parallel and sequential faults that will result in the occurrence of the undesired event. FTA will also demonstrate the links and complex combinations of events which could result in an undesired event. The FTA can enhance the system’s safety by isolating critical components and identifying problem implementations.

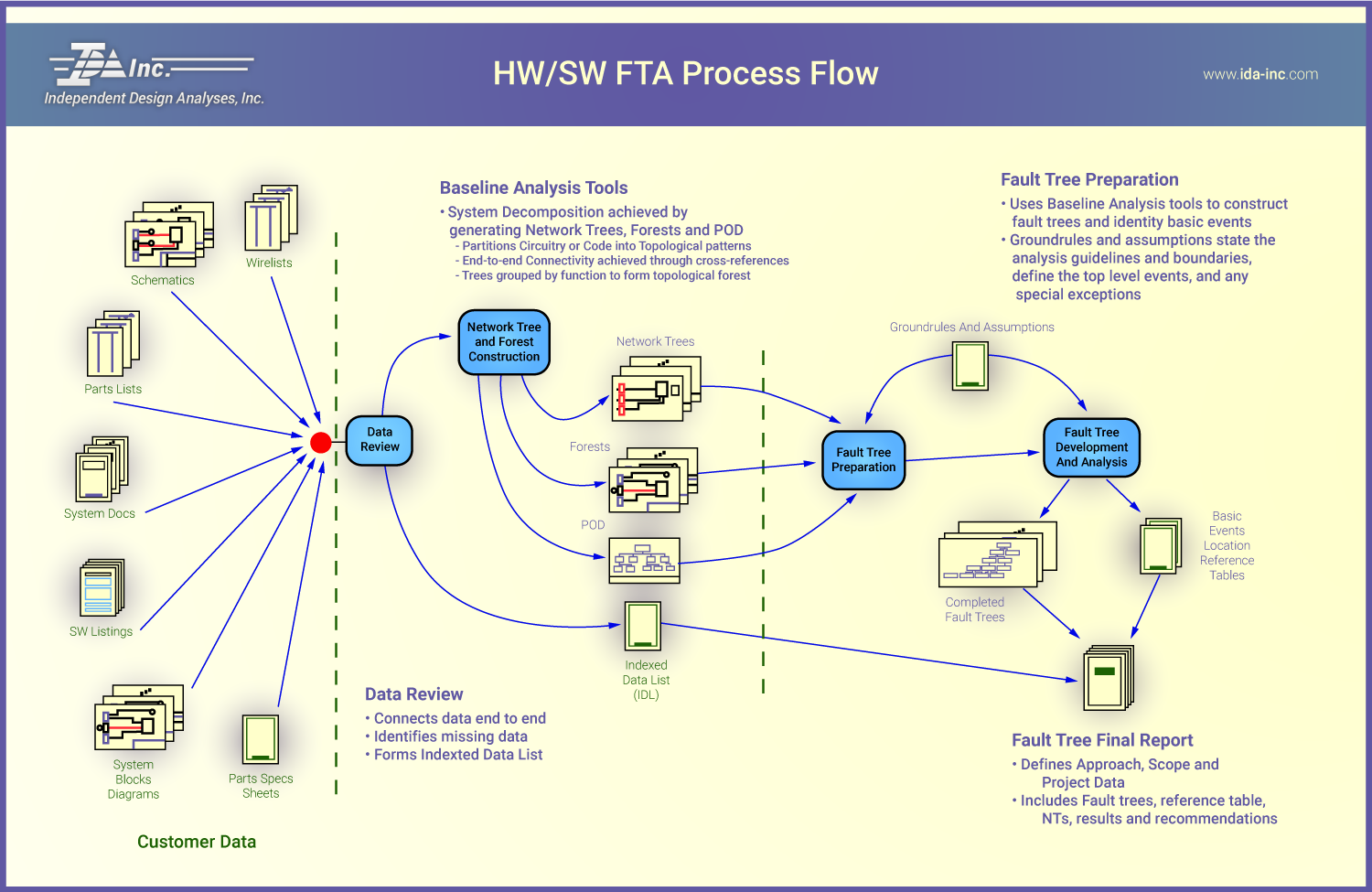

IDA has recently developed the methodology for generating Integrated Hardware/Software Fault-Trees. This new concept incorporates the software logic events implemented by a micro-controller and it’s respective embedded software with system hardware, and shows the relationships between events necessary to produce the undesirable top-level failure. In situations where embedded software controls the system, the interaction of the software logic with the hardware failures must be considered in order to discover all the events that can produce the top-level fault. Many times, as was demonstrated by the recently completed Integrated Fault Trees by IDA, hardware failures on the sensor side of the micro-controller and incorrect commands/status from other embedded processors generated failure events within the Fault Tree because of software logic interaction with the hardware. These failures would not have been detected or detailed in a hardware-only Fault Tree. The Integrated Fault Trees lead to some important software changes that increased the system’s fault-tolerance and provided a tool to the Reliability Department for assessing future changes.